Buffer Optimization Techniques . From selection to optimization, this article. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. uncover the significance of effective buffer management in scientific studies. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first.

from www.slideserve.com

uncover the significance of effective buffer management in scientific studies. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. From selection to optimization, this article.

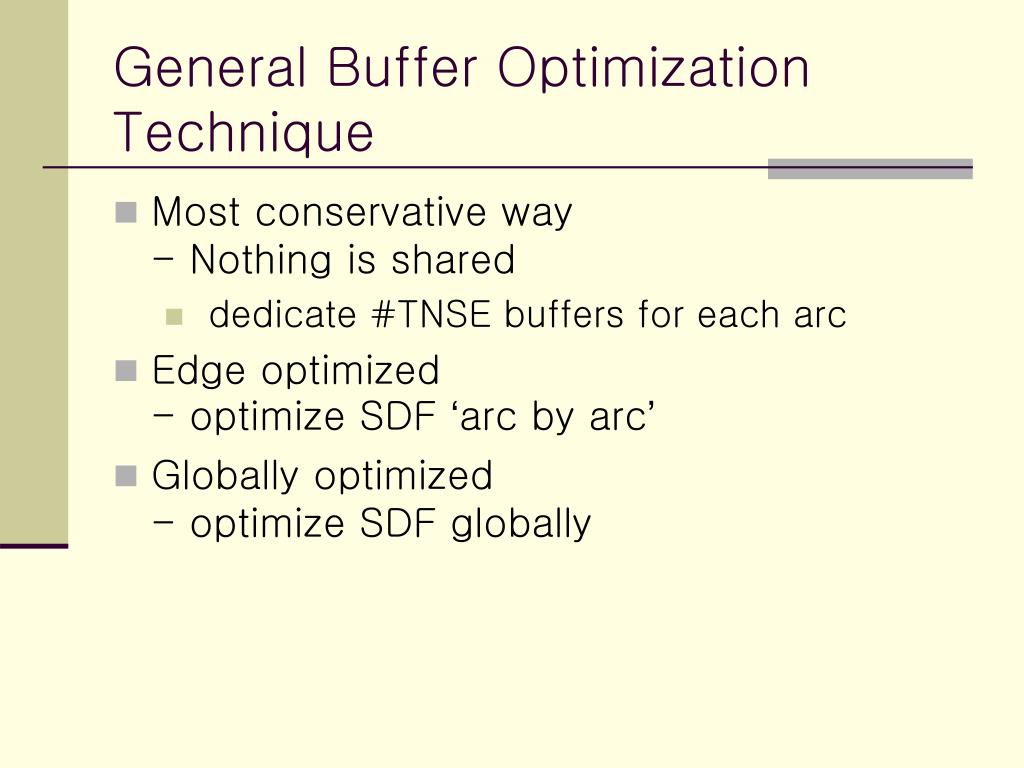

PPT Buffer Issues of Hardware synthesis from SDF graph PowerPoint

Buffer Optimization Techniques the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. uncover the significance of effective buffer management in scientific studies. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. From selection to optimization, this article. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first.

From www.slideserve.com

PPT Buffer Issues of Hardware synthesis from SDF graph PowerPoint Buffer Optimization Techniques From selection to optimization, this article. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. uncover the significance of effective buffer management in scientific studies. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. we introduce here a new strategy to buffer optimization, based. Buffer Optimization Techniques.

From present5.com

Chapter 5 Input Output 5 1 Principles of I O Buffer Optimization Techniques we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. uncover the significance of effective buffer management in scientific studies. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. accurate preparation and correct selection of buffers is essential to obtain reproducible. Buffer Optimization Techniques.

From www.slideserve.com

PPT ZBuffer Optimizations PowerPoint Presentation, free download Buffer Optimization Techniques accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. we introduce here a new. Buffer Optimization Techniques.

From dino-software.com

Mysteries of VSAM Batch Buffer Optimization Solved! DinoSoftware Buffer Optimization Techniques accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. From selection. Buffer Optimization Techniques.

From www.slideserve.com

PPT Buffer Issues of Hardware synthesis from SDF graph PowerPoint Buffer Optimization Techniques uncover the significance of effective buffer management in scientific studies. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. From selection to optimization, this article. algorithms use several design optimization techniques. Buffer Optimization Techniques.

From www.slideserve.com

PPT ZBuffer Optimizations PowerPoint Presentation, free download Buffer Optimization Techniques algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. uncover the significance of effective buffer management in scientific studies. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. we introduce here a new strategy to buffer optimization, based on a parametric study of. Buffer Optimization Techniques.

From www.slideserve.com

PPT Techniques for VLSI Circuit Optimization Considering Process Buffer Optimization Techniques From selection to optimization, this article. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. algorithms. Buffer Optimization Techniques.

From www.semanticscholar.org

Figure 1 from PCR buffer optimization with uniform temperature regimen Buffer Optimization Techniques accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. we introduce here a new strategy to. Buffer Optimization Techniques.

From www.researchgate.net

a Buffer system optimization for purified NHase of mutant. b Ionic Buffer Optimization Techniques the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. uncover the significance of effective buffer management in scientific studies. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. algorithms use several design optimization techniques such as buffer insertion, gate sizing,. Buffer Optimization Techniques.

From www.researchgate.net

Slide−buffer optimization of CV and SNR for five SMs with 29 different Buffer Optimization Techniques the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. From selection to optimization, this article. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. uncover. Buffer Optimization Techniques.

From www.researchgate.net

(PDF) Optimization of buffer sizes in assembly systems using Buffer Optimization Techniques the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. uncover the significance of effective buffer management in scientific studies. algorithms use several design optimization techniques such as buffer insertion, gate sizing,. Buffer Optimization Techniques.

From www.researchgate.net

(PDF) QueueBuffer Optimization Based on Aggressive Random Early Buffer Optimization Techniques we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. From selection to optimization, this article. uncover the significance of effective buffer management in scientific studies. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. algorithms use several design optimization. Buffer Optimization Techniques.

From www.slideserve.com

PPT Buffer Issues of Hardware synthesis from SDF graph PowerPoint Buffer Optimization Techniques From selection to optimization, this article. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. we introduce here a new strategy to buffer optimization, based on a parametric study of the. Buffer Optimization Techniques.

From www.slideserve.com

PPT ZBuffer Optimizations PowerPoint Presentation, free download Buffer Optimization Techniques we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. From selection to optimization, this article. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. . Buffer Optimization Techniques.

From www.researchgate.net

Buffer conditions optimization of the TRF assay for C0C2 binding to Buffer Optimization Techniques accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. From selection to optimization, this article. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. uncover the significance of effective buffer management in scientific studies. algorithms use several design optimization. Buffer Optimization Techniques.

From www.witec.ch

Immobilization Buffer Optimization Kit Witec AG Buffer Optimization Techniques From selection to optimization, this article. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. uncover the significance of effective. Buffer Optimization Techniques.

From www.researchgate.net

Invertase enzyme activity and amplification buffer optimization. (A Buffer Optimization Techniques we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. algorithms use several design optimization techniques such as buffer insertion, gate sizing, commutative pin swapping, gate. uncover the significance of effective buffer management in scientific studies. accurate preparation and correct selection of buffers is essential to. Buffer Optimization Techniques.

From pipettejockey.com

Mashup RT Update 2 Our Take on Purification/Activity Assays/Buffer Buffer Optimization Techniques the proposed clock tree optimization methodologies reduce the power dissipation without any impact on. accurate preparation and correct selection of buffers is essential to obtain reproducible and consistent results. From selection to optimization, this article. we introduce here a new strategy to buffer optimization, based on a parametric study of the roots of the first. algorithms. Buffer Optimization Techniques.